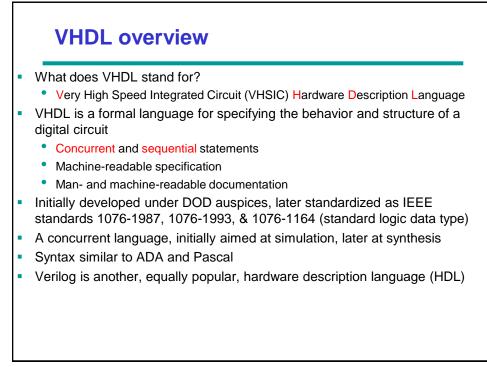

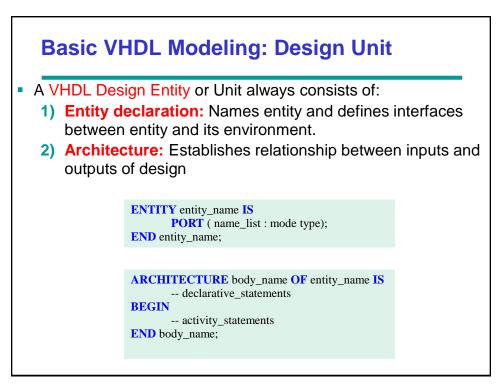

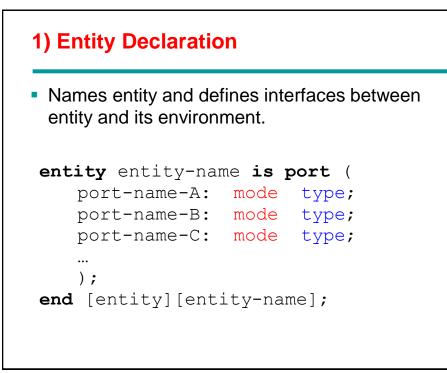

## Outline VHDL Overview Basic VHDL Modelling Institute declaration Architecture declaration Structural vs. Behavioural Description Combinational, Sequential Testbenches Resources

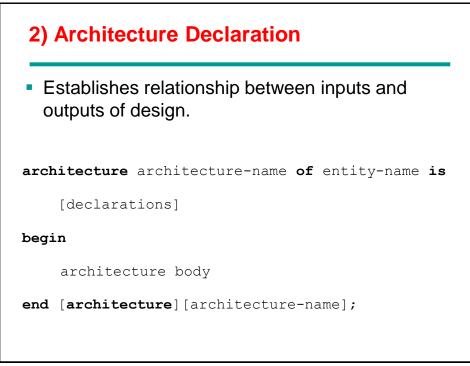

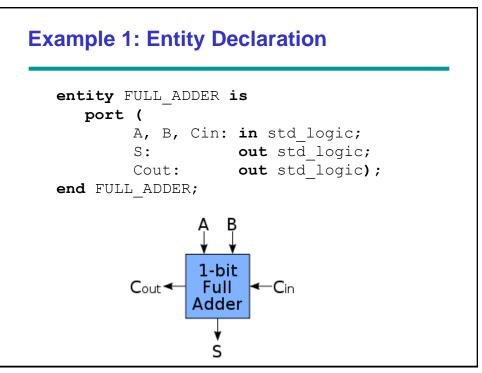

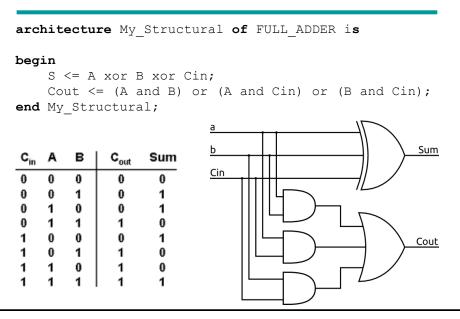

## **Example 1: Architecture Declaration**

```

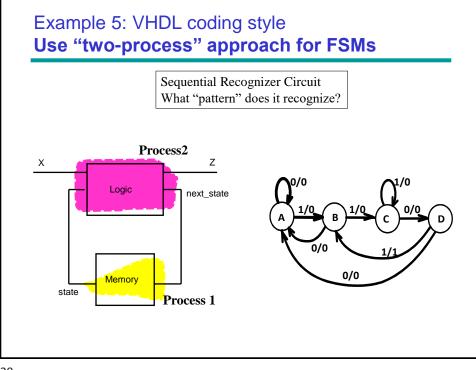

-- process 1: implements positive edge-triggered

-- flip-flop with asynchronous reset

state_register: process (CLK, RESET)

begin

if (RESET = '1') then

state <= A;

elsif (CLK'event and CLK = '1') then

state <= next_state;

end if;

end process;

-- continue on next slide...

```

```

-- process 2: Z and next_state implemented

-- as functions of input X and state

X_and_next_state_functions: process (X, state)

begin

case state is

when A =>

Z <= '0';

if X = '1' then next_state <= B;</pre>

else next state <= A;

end if;

when B =>

Z <= '0';

if X = '1' then next_state <= C;</pre>

else next state <= A;

end if;

when C =>

z <= '0';

if X = '1' then next_state <= C;</pre>

else next_state <= D;</pre>

end if;

when D =>

if X = '1' then Z <= '1'; next_state <= B;</pre>

else Z <= `0'; next_state <= A;</pre>

end if;

end case;

end process;

end architecture;

```