**Cache Example** 8-blocks, 1 word/block, direct mapped Initial state Index V Tag Data 000 Ν 001 Ν 010 Ν 011 Ν 100 Ν 101 Ν 110 Ν 111 Ν 28

|            |        | kamp     | )le | )        |             |

|------------|--------|----------|-----|----------|-------------|

| Word       | addr.  | Binary a | ddr | Hit/miss | Cache block |

| 22         | 2      | 10 110   | )   | Miss     | 110         |

| 000<br>001 | N<br>N |          |     |          |             |

| Index      | V      | Tag      | Dat | а        |             |

| 001        | N      |          |     |          |             |

| 010        | Ν      |          |     |          |             |

| 011        | Ν      |          |     |          |             |

| 011        | N      |          |     |          |             |

| 100        | 1      |          |     |          |             |

| -          | N      |          |     |          |             |

| 100        |        | 10       | Ме  | m[10110] |             |

| vvora | addr | Binary a | addr | Hit/miss | Cache block |

|-------|------|----------|------|----------|-------------|

| 20    |      | 11 01    |      | Miss     | 010         |

| Index | V    | Tag      | Dat  | а        |             |

| 000   | N    |          |      |          |             |

| 001   | N    |          |      |          |             |

| 010   | Υ    | 11       | Me   | m[11010] |             |

| 011   | N    |          |      |          |             |

| 100   | N    |          |      |          |             |

| 101   | Ν    |          |      |          |             |

| 110   | Y    | 10       | Me   | m[10110] |             |

| 110   |      |          |      |          |             |

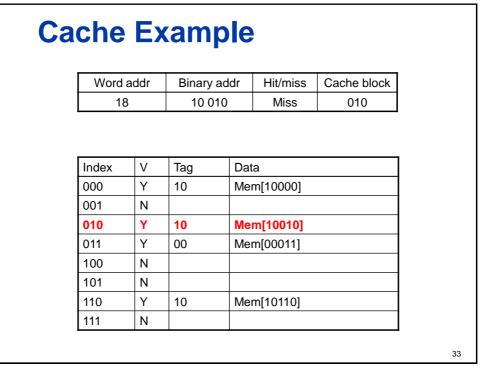

## **Cache Example**

| Word addr | Binary addr | Hit/miss | Cache block |

|-----------|-------------|----------|-------------|

| 22        | 10 110      | Hit      | 110         |

| 26        | 11 010      | Hit      | 010         |

| Index | V | Tag | Data       |  |

|-------|---|-----|------------|--|

| 000   | N |     |            |  |

| 001   | N |     |            |  |

| 010   | Y | 11  | Mem[11010] |  |

| 011   | N |     |            |  |

| 100   | Ν |     |            |  |

| 101   | N |     |            |  |

| 110   | Y | 10  | Mem[10110] |  |

| 111   | N |     |            |  |

| Word  | addr | Binary | addr | Hit/miss | Cache block |

|-------|------|--------|------|----------|-------------|

| 1     |      | 10 0   |      | Miss     | 000         |

| 3     | -    | 00 0   |      | Miss     | 011         |

| 1     | 6    | 10 (   |      | Hit      | 000         |

| Index | V    | Tag    | Dat  | а        |             |

| 000   | Υ    | 10     | Ме   | m[10000] |             |

| 001   | N    |        |      |          |             |

| 010   | Y    | 11     | Me   | m[11010] |             |

| 011   | Y    | 00     | Ме   | m[00011] |             |

| 100   | N    |        |      |          |             |

| 101   | N    |        |      |          |             |

| 110   | Y    | 10     | Me   | m[10110] |             |

| 111   | N    |        |      |          |             |

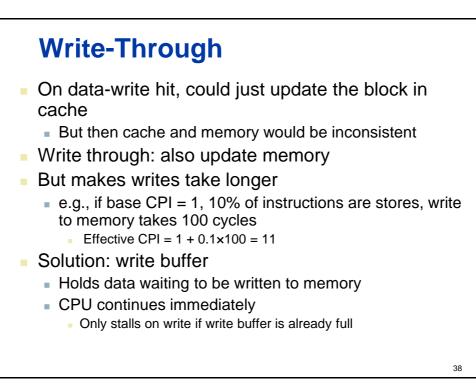

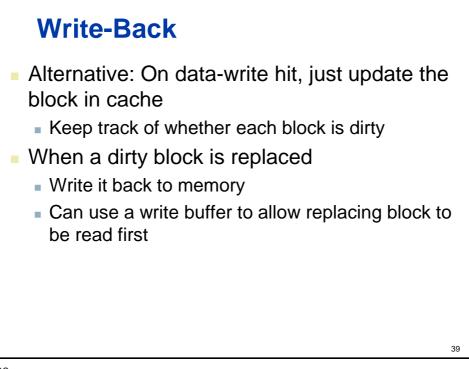

| Q4: What Ha                                      | appens on a Write                                                                                    | e?                                                                                                                                |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                                  | Write-Through                                                                                        | Write-Back                                                                                                                        |

| Policy                                           | <ul> <li>Data written to cache<br/>block</li> <li>Also written to lower-<br/>level memory</li> </ul> | <ul> <li>Write data only to<br/>the cache block</li> <li>Update lower leve<br/>when a block falls<br/>out of the cache</li> </ul> |

| Debug                                            | Easy                                                                                                 | Hard                                                                                                                              |

| Do read misses<br>produce writes?                | No                                                                                                   | Yes                                                                                                                               |

| Do repeated<br>writes make it to<br>lower level? | Yes                                                                                                  | No                                                                                                                                |

|                                                  | •                                                                                                    |                                                                                                                                   |

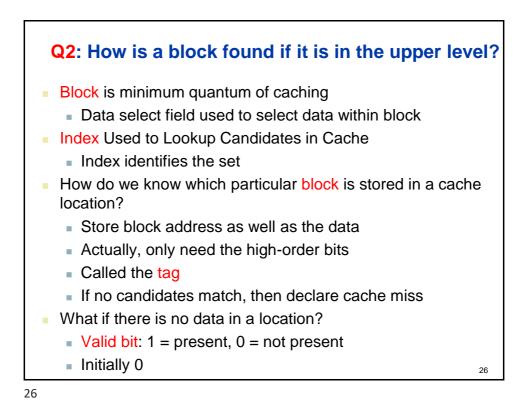

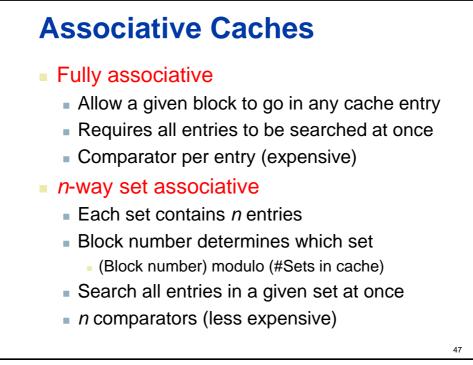

## 2) Finding a Block

| Associativity            | Location method                               | Tag comparisons |

|--------------------------|-----------------------------------------------|-----------------|

| Direct mapped            | Index                                         | 1               |

| n-way set<br>associative | Set index, then search entries within the set | n               |

| Fully associative        | Search all entries                            | #entries        |

|                          | Full lookup table                             | 0               |

- Hardware caches

- Reduce comparisons to reduce cost

- Virtual memory

- Full table lookup makes full associativity feasible

75

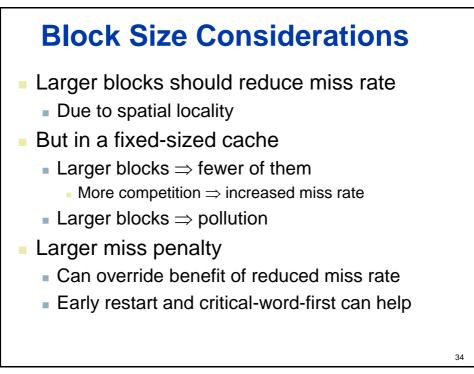

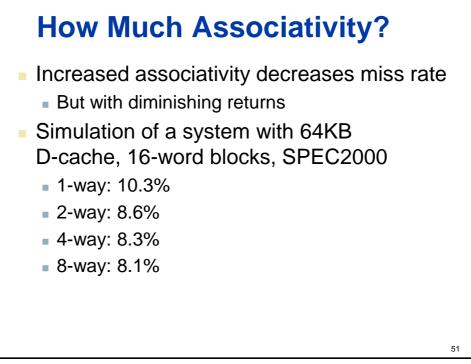

Benefit in reduced miss rate

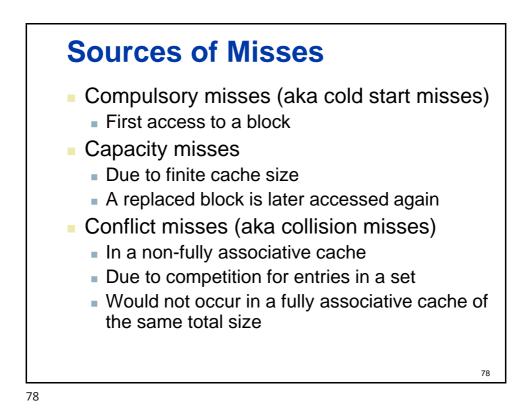

## **Cache Design Trade-offs**

| Design change          | Effect on miss rate           | Negative performance effect                                                                             |

|------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------|

| Increase cache size    | Decrease capacity<br>misses   | May increase access time                                                                                |

| Increase associativity | Decrease conflict<br>misses   | May increase access time                                                                                |

| Increase block size    | Decrease compulsory<br>misses | Increases miss<br>penalty. For very large<br>block size, may<br>increase miss rate<br>due to pollution. |

79

## **Cache Coherence Problem** Suppose two CPU cores share a physical address space Write-through caches Event CPU A's CPU B's Time Memory step cache cache 0 0 1 CPU A reads X 0 0 2 CPU B reads X 0 0 0 3 CPU A writes 1 to X 1 0 1 80