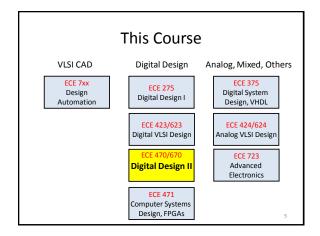

### ECE-470 – Digital Design II Introduction

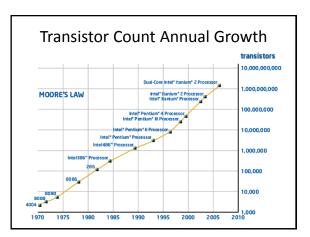

|                       | 1997 -2001  | 2003 - 2006 |

|-----------------------|-------------|-------------|

| Feature size (micron) | 0.25 - 0.15 | 0.13 - 0.10 |

| Transistors/sq. cm    | 4 - 10M     | 18 - 39M    |

| Pin count             | 100 - 900   | 160 - 1475  |

| Clock rate (MHz)      | 200 - 730   | 530 - 1100  |

| Power (Watts)         | 1.2 - 61    | 2 - 96      |

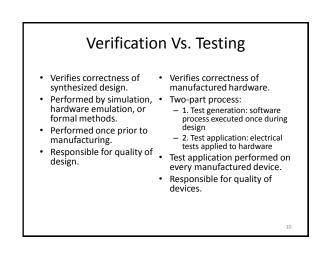

## Verification Vs. Testing: Definitions

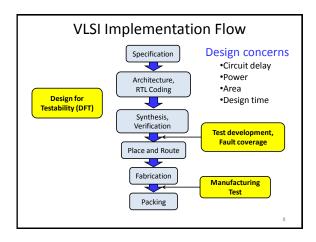

- Design synthesis: Given an I/O function, develop a procedure to manufacture a device using known materials and processes.

- Verification: Predictive analysis to ensure correctness of the synthesized design; when manufactured, will perform the given I/O function.

- Test: Manufacturing step that ensures that the physical device, manufactured from the synthesized design, has no manufacturing defect.

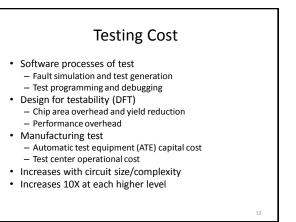

### Cost of Manufacturing Testing (2000)

- 0.5-1.0GHz, analog instruments,1,024 digital pins: ATE purchase price

- = \$1.2M + 1,024 x \$3,000 = \$4.272M

- Running cost (five-year linear depreciation)

= Depreciation + Maintenance + Operation

- = \$0.854M + \$0.085M + \$0.5M

- = \$1.439M/year

- Test cost (24 hour ATE operation)

\$1.439M/(365 x 24 x 3,600)

- = 4.5 cents/second

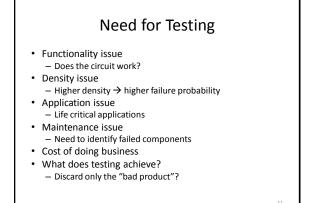

### Levels of Testing

- Levels

- Chip

- Board

- System

- Boards put together

- System-on-Chip (SoC)

- System in field

- Rule of 10: It costs 10 times more to test a device as we move to higher level in the product manufacturing process

# Levels of Testing

- Other ways to define levels these are important to develop correct "fault models" and "simulation models"

- Transistor

- Gate

- RTL

- Functional

- Behavioral

- Architecture

- Focus in this course: Chip level testing gate level design

15

### **Role of Testing**

- Detection: Determination whether or not the device under test (DUT) has some fault.

- Diagnosis: Identification of a specific fault that is present on DUT.

- Device characterization: Determination and correction of errors in design and/or test procedure.

- Failure mode analysis (FMA): Determination of manufacturing process errors that may have caused defects on the DUT.

#### 16

14

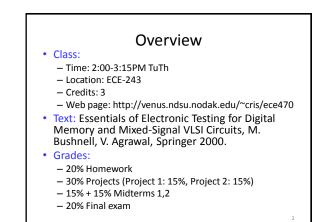

### Overview

- PART 1: Test generation

- Test economics, Fault models, Fault simulation, Combinational, sequential ATPG, Memory test, IDDQ test.

- PART 2: Design for testability (DFT)

- DFT refers to hardware design styles or added hardware that reduces test generation complexity.

- Scan design, BIST.

- System test