# **Lab 3: Four-Bit Binary Counter**

EE-459/500 HDL Based Digital Design with Programmable Logic Electrical Engineering Department, University at Buffalo Last update: Cristinel Ababei, August 2012

### 1. Objective

The objective of this lab is to design and test a 4-bit binary counter. Aside from learning about the on-board clock signal and push-buttons as well as about frequency dividers, this lab reinforces the design flow steps introduced in the previous labs.

## 2. Description

We design a 4-bit binary counter. Our counter has an output "Q" with four bits. During correct operation, the counter starts at "0000" and then binary counts up to output "0001", "0010", "0011", and so on until it outputs "1111", after which it resets to "0000" and starts again. The first implementation of our counter has only one input: a clock signal CK. The clock signal is provided by the external (to the FPGA) clock generator. We use the output Q to drive the first four LEDs on the Atlys board.

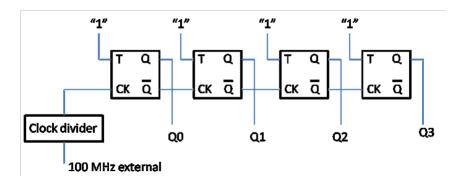

The block diagram of the simplest/basic structural implementation of such a binary counter is shown in the next figure. This implementation is known as a ripple counter.

Figure 1 Block diagram of a 4-bit binary counter

#### **Toggle Flip-Flop**

As shown in the figure above, we use four Toggle Flip-Flops (TFF's). As you remember, the operation of a TFF is as follows: When the "T" input is logic "1", the output "Q" will toggle on each clock transition. When the "T" input is logic "0", the output "Q" will not change.

To start our design, we first create a new project by launching Xilinx ISE WebPack and following the steps discussed in lab 2. Call the new project **fourbit\_counter** and select the same location where you created the previous project.

Create and add to the project a first VHDL file called **tff.vhd** with the following content:

<sup>--</sup> tff.vhd

<sup>--</sup> Toggle Flip-Flop with behavioral description

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity tff is

Port ( T : in STD_LOGIC;

CK : in STD LOGIC;

Q, QN : out STD LOGIC);

end tff;

architecture My behavioral of tff is

signal mem : std logic := '0';

begin

process (CK, T, mem) -- execute this process only when the clock changes

begin

if T = '0' then null; -- no toggle, so do nothing

elsif (CK'event and CK = '1') then

mem <= not mem; -- rising edge of clock and T = 1, toggle stored value

end if;

end process;

Q \ll mem;

QN <= not mem;

end;

```

#### Clock Divider

Our counter uses as a clock a signal generated by the on-board clock generator. This clock generator is a single 100 MHz CMOS oscillator on the Atlys board connected to pin L15 of the Spartan-6 FPGA. Because the frequency of 100 MHz is too high for the human eye to be able to see how the counter output drives the LEDs, we must utilize a clock divider to lower the frequency to about 1 Hz.

Create and add to the project a second VHDL file called **ck\_divider.vhd** with the following content:

```

-- ck divider.vhd

-- This is a clock divider. It takes as input a signal

-- of 100 MHz and generates an output as signal with a frequency

-- of about 1 Hz.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity ck divider is

Port ( CK IN : in STD LOGIC;

CK OUT : out STD LOGIC);

end ck divider;

architecture Behavioral of ck divider is

constant TIMECONST : integer := 84;

signal count0, count1, count2, count3 : integer range 0 to 1000;

signal D : std logic := '0';

begin

process (CK IN, D)

```

```

begin

if (CK IN'event and CK IN = '1') then

count0 <= count0 + 1;</pre>

if count0 = TIMECONST then

count0 <= 0;

count1 <= count1 + 1;</pre>

elsif count1 = TIMECONST then

count1 <= 0;

count2 <= count2 + 1;</pre>

elsif count2 = TIMECONST then

count2 <= 0;

count3 <= count3 + 1;</pre>

elsif count3 = TIMECONST then

count3 <= 0;

D \le not D;

end if;

end if;

CK OUT <= D;

end process;

end Behavioral;

```

Read the above code to understand its operation. It takes the 100 MHz external clock as input CK\_IN and generates an output signal CK\_OUT of 1 Hz. The output frequency is adjustable according to the following formula (TIMECONST = 84 in this case in order to get an output frequency of about 1 Hz):

```

Output Frequency = 100000000 / (2 * (TIMECONST ^ 4))

```

**Note:** There are other ways of implementing the TFF or the clock divider. In time, by accumulating more and more experience, you will develop your own VHDL programming style by adopting different coding techniques.

### 4-bit Binary Counter

Finally, let's create a third VHDL file with the top-level description of our fourbit\_counter design described in Figure 1. Create and add to the project the third VHDL file called **fourbit\_counter.vhd** with the following content:

```

-- fourbit_counter.vhd

-- This is a simple 4-bit (Ripple) binary counter made up

-- of four T flip-flops. It also includes a clock divider

-- to bring down the input CK signal from 100 MHz to about 1 Hz.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity fourbit_counter is

Port ( CK : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR (3 downto 0));

end fourbit_counter;

architecture Structural of fourbit_counter is

component tff

```

```

Port ( T : in STD_LOGIC;

CK : in STD LOGIC;

Q, QN : out STD LOGIC);

end component;

component ck divider

Port ( CK IN : in STD LOGIC;

CK OUT : out STD LOGIC);

end component;

signal all T, S0, S1, S2, S3, internal ck : STD LOGIC;

begin

-- We use signal all T set to logic '1' to drive

-- input T of all T flip-flops to logic '1'.

all T <= '1';

CLOCK: ck divider port map (CK, internal ck);

TFF0: tff port map (all T, internal ck, Q(0), S0);

TFF1: tff port map (all T, S0, Q(1), S1);

TFF2: tff port map (all T, S1, Q(2), S2);

TFF3: tff port map (all T, S2, q(3), S3);

end Structural;

```

### **Design Implementation**

At this time, we have coded the entire design and its components. Before continuing to Design Implementation, we first take care of two things:

- Set the fourbit\_counter as the top-level design (we need to do this because currently TFF.vhd is the top-level because it was added first to the project). To do that, in the Hierarchy window, Right click on "fourbit counter Structural (fourbit counter.vhd)" and select Set as To-Level.

- Pin assignment. As discussed earlier we use the external clock signal connected to pin **L15** of the Spartan-6 FPGA. So, we assign pin L15 to the input "CK" of our design. Also, we use the output "Q" of our design to drive the first four LEDs of the Atlys board. Now, do the pin assignment as learned in lab 2. After this step, your UCF file should have the following content:

```

# PlanAhead Generated physical constraints

NET "Q[0]" LOC = U18;

NET "Q[1]" LOC = M14;

NET "Q[2]" LOC = N14;

NET "Q[3]" LOC = L14;

NET "CK" LOC = L15;

```

We are now ready to implement the design: in the Processes tab double-click Implement Design (or right-click on Implement Design and select Run).

### Generate the Programming File and Program the FPGA

Double-click on Generate Programming File in the Process tab. Then, program the FPGA using the Adept software as learned in lab 2. Verify that our counter works correctly.

## 3. Lab assignment

### Lab preparation

A major problem with the counter implemented in this lab is that the individual flip-flops do not all change state at the same time. Rather, each flip-flop is used to trigger the next one in the series. Thus, in switching from all 1s (count = 15) to all 0s (count wraps back to 0), we don't see a smooth transition. Instead, output Q(0) falls first, changing the apparent count to 14. This triggers output Q(1) to fall, changing the apparent count to 12. This in turn triggers output Q(2), which leaves a count of 8 while triggering output Q(3) to fall. This last action finally leaves us with the correct output count of zero. We say that the change of state "ripples" through the counter from one flip-flop to the next. Therefore, this circuit is known as a "ripple counter".

This causes no problem if the output is only to be read by human eyes; the ripple effect is too fast for us to see it. However, if the count is to be used as a selector by other digital circuits (such as a multiplexer or demultiplexer), the ripple effect can easily allow signals to get mixed together in an undesirable fashion. To prevent this, we need to devise a method of causing all of the flip-flops to change state at the same moment. That would be known as a "**synchronous counter**" because the flip-flops would be synchronized to operate in unison.

In this lab assignment, you must design a synchronous counter version of our fourbit\_counter to arrive to a new block diagram, where all flip-flops are driven by the same clock signal. You should design this counter using the Karnaugh Maps method and utilize JK flip-flops instead of T flip-flops. In addition, the top-level design of the fourbit\_counter should have an additional input, "RESET", which when set to logic "1" forces the counter to the initial state "0000". The RESET input should be controlled by one of the pushbuttons of the Atlys board.

#### **Optional:**

- Remove entirely the clock divider from the design. Instead of the clock signal of 100 MHz utilize a signal from one of the pushbuttons of the Atlys board. In this case, the counter will advance each time the pushbutton is pressed.

- Modify the counter such that it can be told to count up or down.

#### Lab report and demo

You must turn-in a lab report, which should contain the following:

- Lab title

- Your name

- Introduction section a brief description of the problem you solve in this lab assignment, outlining the goal and design requirements.

- Solution details of your Karnaugh Maps method. Include all block diagrams and K-maps you need to illustrate each step. This section **must be hand-written**.

- VHDL code of your entire design. Use smaller font to save space.

- Conclusion describe your results and any issues you may have faced during this assignment and how

you solved them.

- For full credit, you must demo the correct operation of your counter to the TA during the next lab.