# EE 459/500 – HDL Based Digital Design with Programmable Logic

# Lecture 4 Introduction to VHDL

Read before class: Chapter 2 from textbook (first part)

### Outline

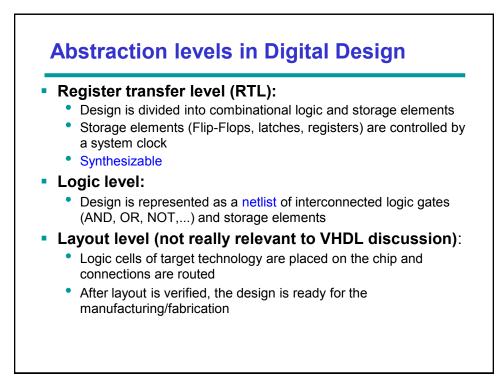

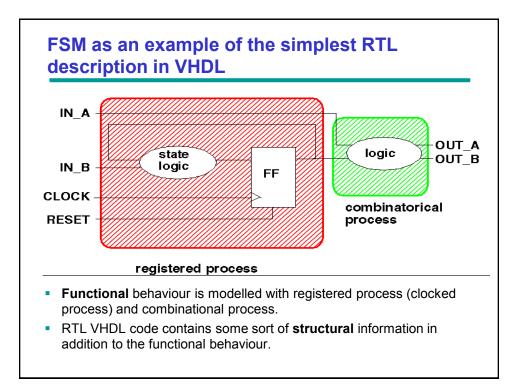

- VHDL Overview

- VHDL Characteristics and Concepts

- Basic VHDL modelling

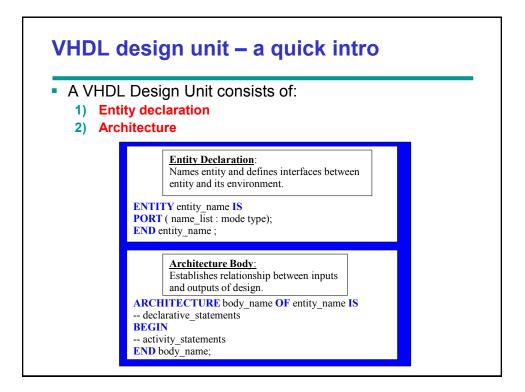

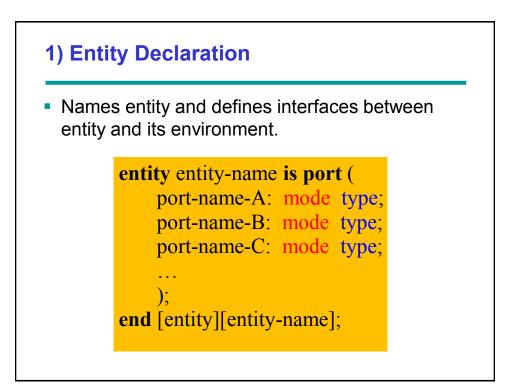

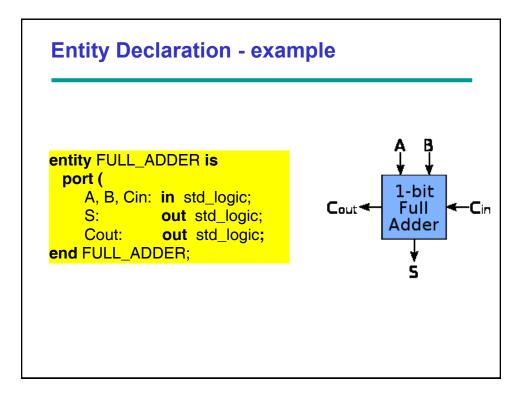

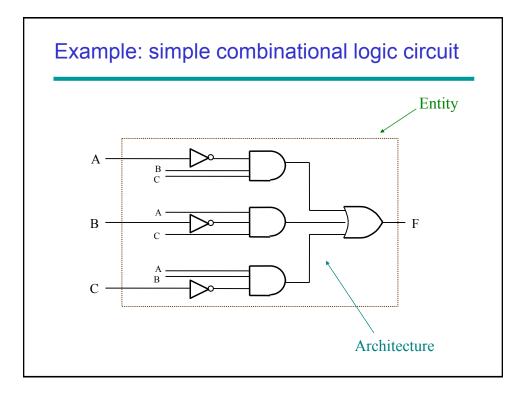

- Entity declaration

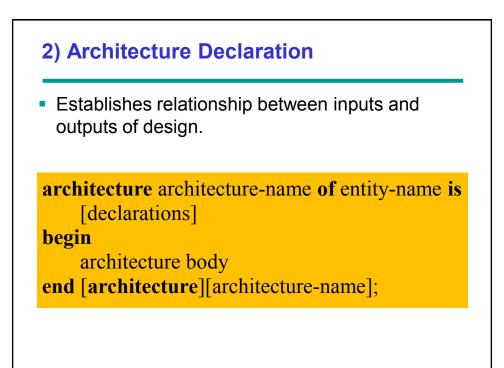

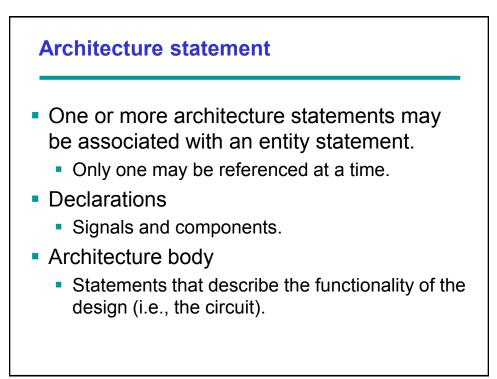

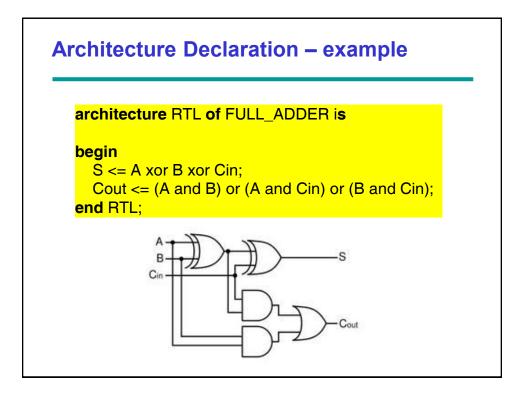

- Architecture declaration

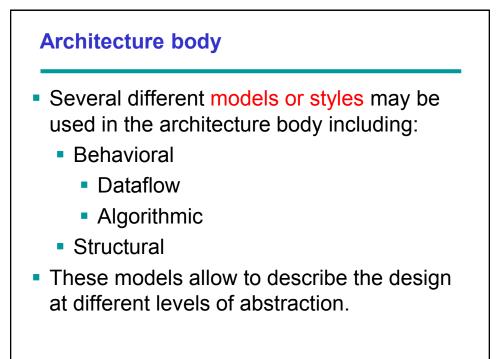

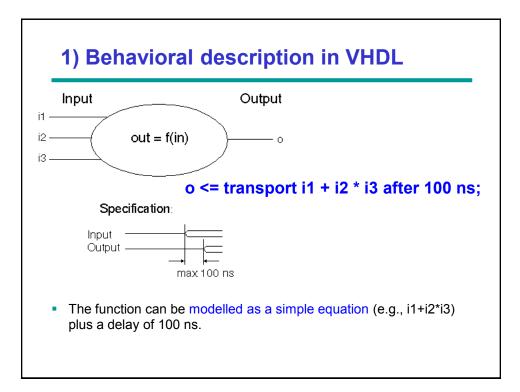

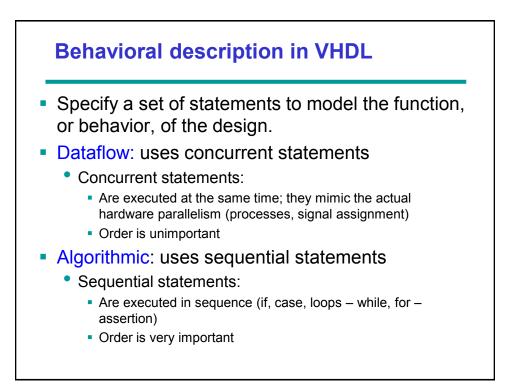

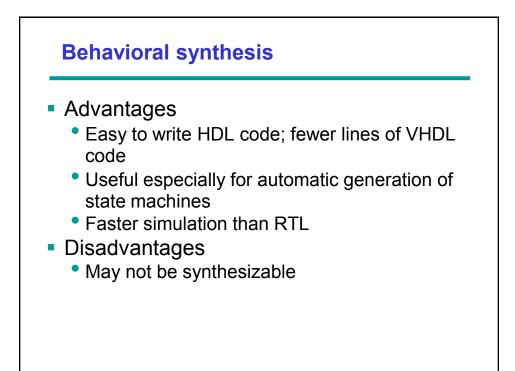

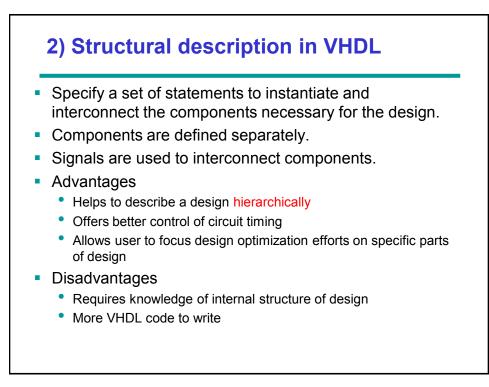

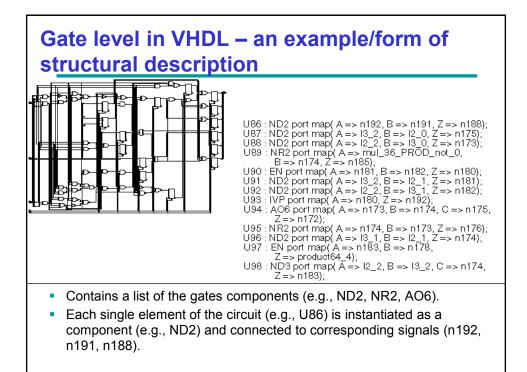

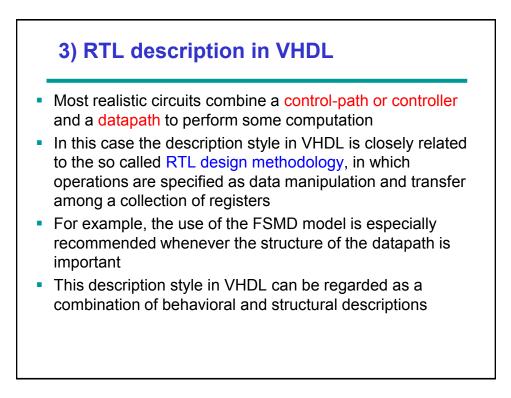

- Behavioural vs. Structural description in VHDL

### Example: entity

```

entity comb_logic_ckt_1 is

Port ( A,B,C : in STD_LOGIC;

F : out STD_LOGIC);

end comb_logic_ckt_1;

```

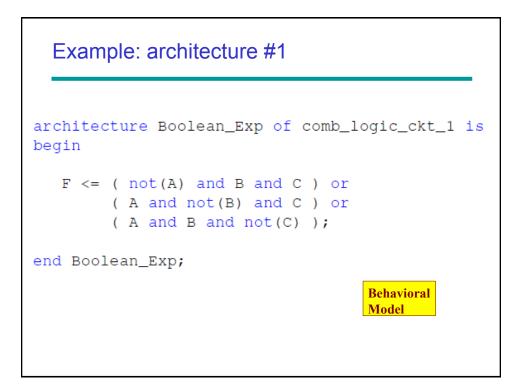

#### Example: architecture #2

```

architecture Truth_table of comb_logic_ckt_1 is

begin

'0'

when ( A = '0' ) and ( B = '0' ) and ( C = '0' ) else

F <=

when (A = '0') and (B = '0') and (C = '1') else

0'

'0'

when (A = '0') and (B = '1') and (C = '0') else

'1'

when (A = '0') and (B = '1') and (C = '1') else

0'

when (A = '1') and (B = '0') and (C = '0') else

when (A = '1') and (B = '0') and (C = '1') else

'1'

'1'

when ( A = '1' ) and ( B = '1' ) and ( C = '0' ) else

'0'

when (A = '1') and (B = '1') and (C = '1') else

'0';

end Truth_table;

Behavioral

Model

```

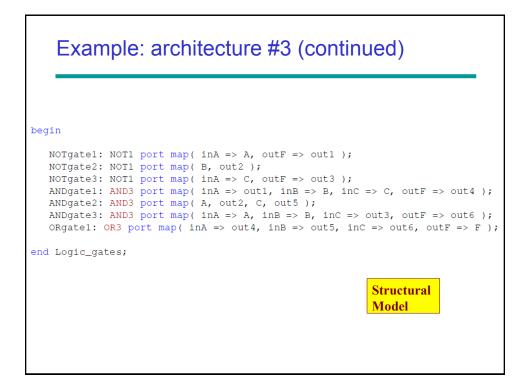

```

Example: architecture #3

architecture Logic_gates of comb_logic_ckt_1 is

-- Component Declarations

-- components are defined in a VHDL package

component AND3

port( inA, inB, inC: in std_logic;

outF: out std_logic );

end component;

component OR3

port( inA, inB, inC: in std_logic;

outF: out std_logic );

end component;

component NOT1

port( inA: in std_logic;

outF: out std_logic );

end component;

-- Signal Declarations

-- used to interconnect the gates in the circuit (i.e. "wires")

signal out1, out2, out3: std_logic;

signal out4, out5, out6: std_logic;

```

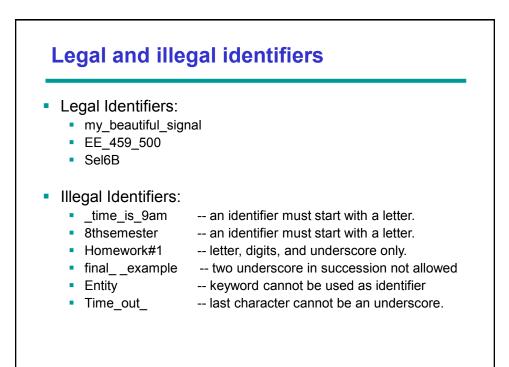

# **VHDL Language & Syntax (Identifier)**

| MySignal_23 normal identifier<br>rdy, RDY, Rdy identical identifiers<br>vector_&_vector X : special character<br>last of Zout X : white spaces<br>idle_state X : consecutive undersco<br>24th_signal X : begins with a numeral<br>open, register X : VHDL keywords |                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>\mySignal_23\ extended identifier</li> <li>\rdy \RDY \Rdy\ different identifiers</li> <li>\vector_&amp;_vector\ legal</li> <li>\last of Zout\ legal</li> <li>\idle_state\ legal</li> <li>\24th_signal\ legal</li> <li>\open \register\ legal</li> </ul>   | <ul> <li>Extended Identifier:</li> <li>Enclosed in back slashes</li> <li>Case sensitive</li> <li>Graphical characters allowed</li> <li>May contain spaced and consecutive underscores.</li> <li>VHDL keywords allowed.</li> </ul> |

| VHDL Reserved Words |            |         |           |            |  |

|---------------------|------------|---------|-----------|------------|--|

| abs                 | disconnect | label   | package   | sla        |  |

| access              | downto     | library | port      | sll        |  |

| after               | else       | linkage | postponed | sra        |  |

| alias               | elsif      | literal | procedure | srl        |  |

| allas               |            |         | •         |            |  |

|                     | end        | loop    | process   | subtype    |  |

| and                 | entity     | map     | protected | then       |  |

| architecture        | exit       | mod     | pure      | to         |  |

| array               | file       | nand    | range     | transport  |  |

| assert              | for        | new     | record    | type       |  |

| attribute           | function   | next    | register  | unaffected |  |

| begin               | generate   | nor     | reject    | units      |  |

| block               | generic    | not     | rem       | until      |  |

| body                | group      | null    | report    | use        |  |

| buffer              | guarded    | of      | return    | variable   |  |

| bus                 | if         | on      | rol       | wait       |  |

| case                | impure     | open    | ror       | when       |  |

| component           | in         | or      | select    | while      |  |

| configuration       | inertial   | others  | severity  | with       |  |

| constant            | inout      | out     | shared    | xnor       |  |

| oonotant            | is         |         | signal    | xor        |  |

### **VHDL** information

- Recommended books on VHDL or the use of VHDL:

- Peter J. Ashenden, The Student's Guide to VHDL, Morgan Kaufmann.

- Peter J. Ashenden, The Designer's Guide to VHDL, Morgan Kaufmann.

- S. Yalamanchili, Introductory VHDL from Simulation to Synthesis, Prentice Hall.

- P.P. Chu, RTL Hardware Design Using VHDL: Coding for Efficiency, Portability and Scalability, Wiley-Interscience, 2006.

- Useful websites see the links provided at:

- http://www.dejazzer.com/ee500/links.html

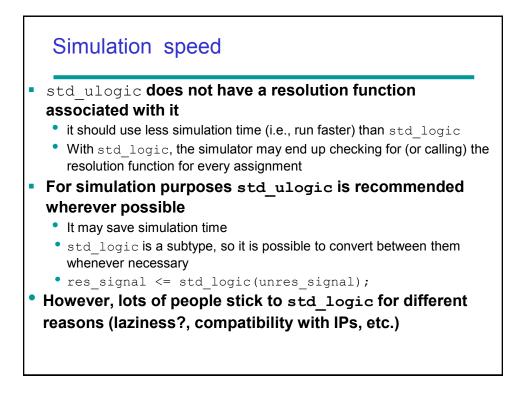

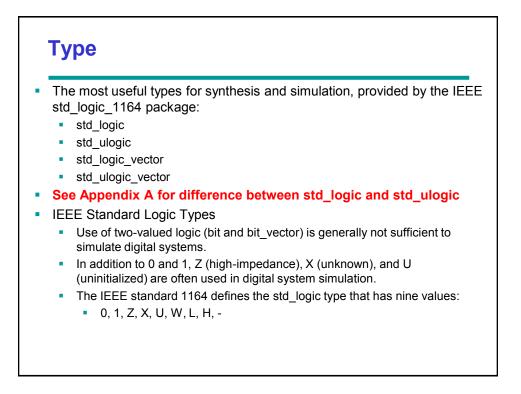

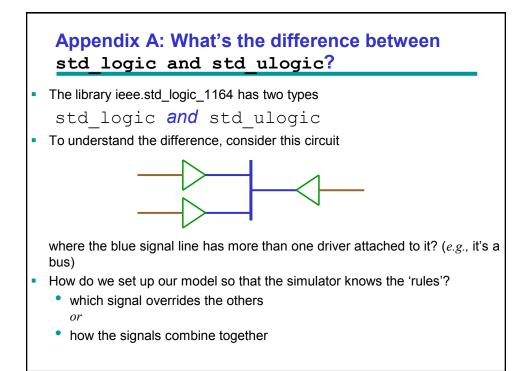

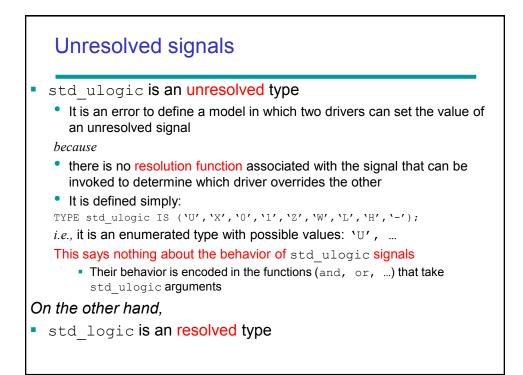

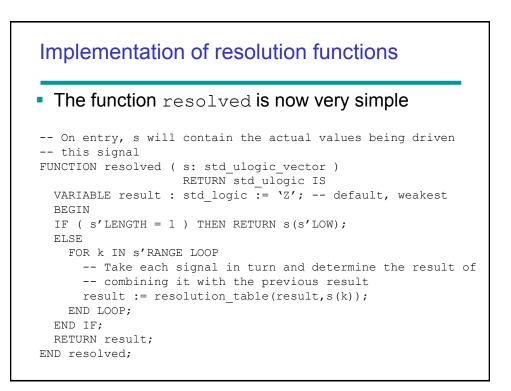

### Unresolved signals

On the other hand,

std logic is an resolved type

It is defined: SUBTYPE std\_logic IS resolved std\_ulogic; Note that there is a function definition just preceding this type:

Thus resolved is a function that takes a vector of std\_ulogic elements and returns a value of std\_ulogic type

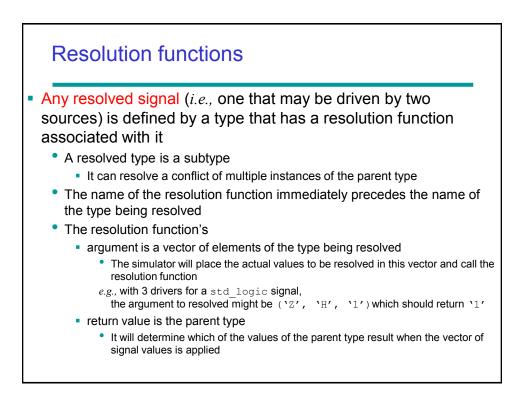

#### This function is called a resolution function

It is called whenever two or more sources (signal assignments) drive a std\_logic signal

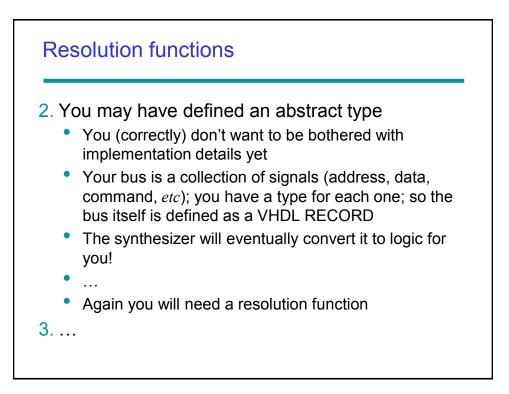

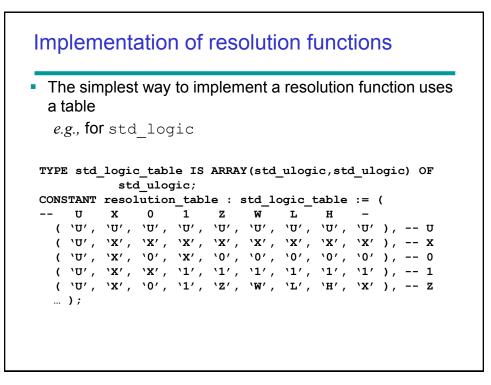

# Writing resolution functions

- You may never need to!

- std\_logic\_1164 defines the most commonly needed one!

#### But,

1. You may be using integer types instead of

- std logic vector in a model of a processor for

- convenience

- speed in simulation

- You will need to define a resolved integer types if your model has a bus with multiple drivers in it

- You will need to have a convention for 'disconnecting' a driver, e.g., setting a driver to emit 0 when it's not driving the bus (where you would drive a 'Z' with std\_logic)

- You can also explicitly disconnect a driver with VHDL's DISCONNECT statement