# Outline

- UART

- CAN

- I2C

- SPI

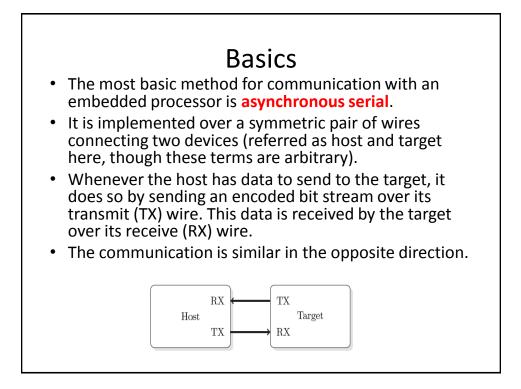

### Basics

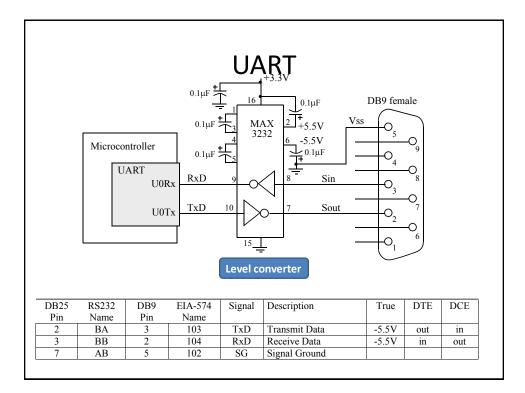

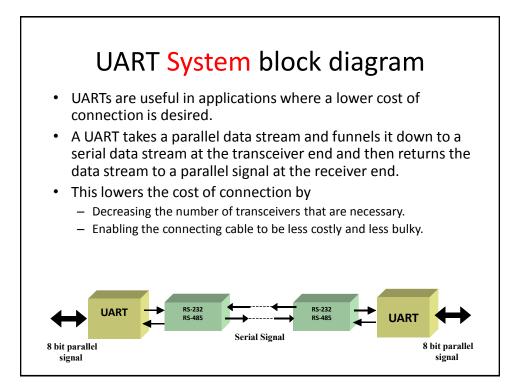

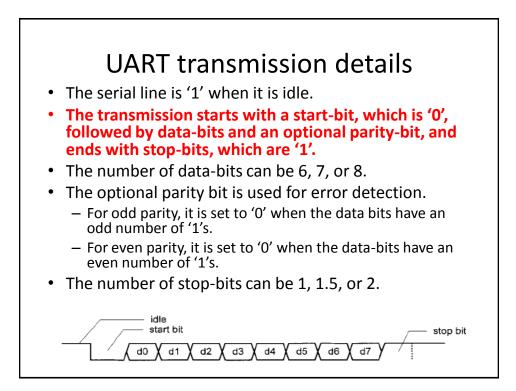

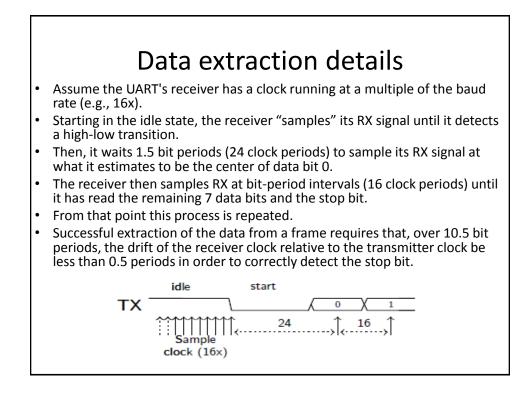

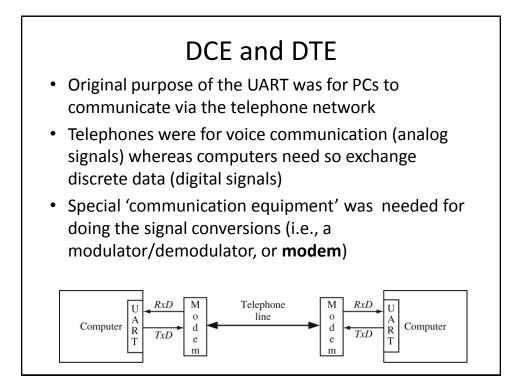

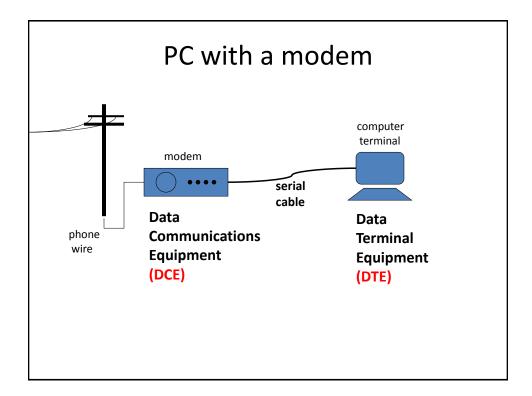

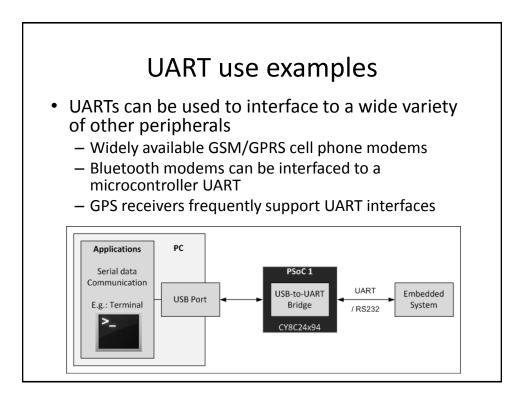

- This mode of communications is called asynchronous because the host and target share no time reference (no clock signal). Instead, temporal properties are encoded in the bit stream by the transmitter and must be decoded by the receiver.

- A commonly used device for encoding and decoding such asynchronous bit streams is a Universal Asynchronous Receiver/Transmitter (UART).

# Outline

- UART

- CAN

- I2C

- SPI

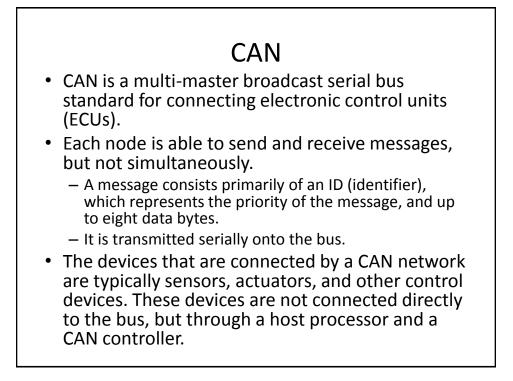

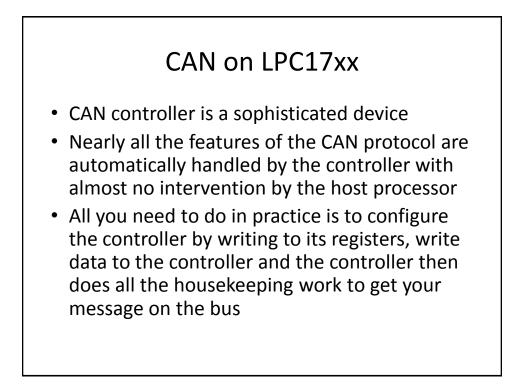

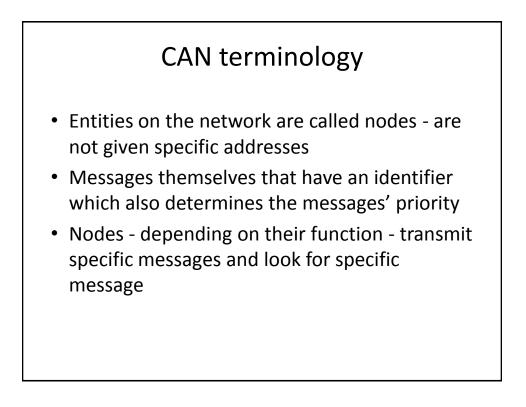

## CAN

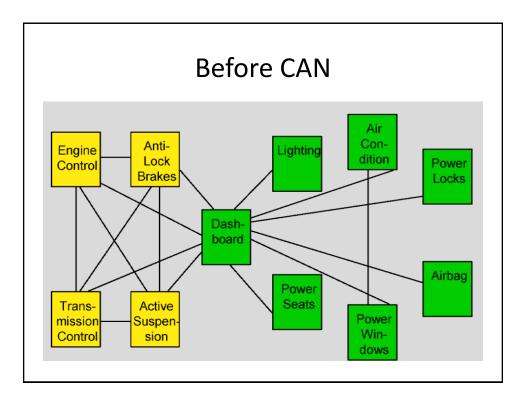

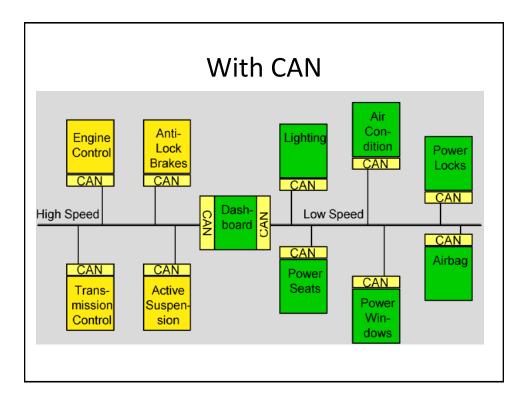

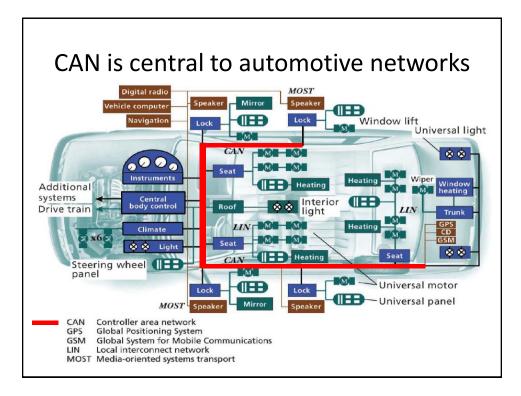

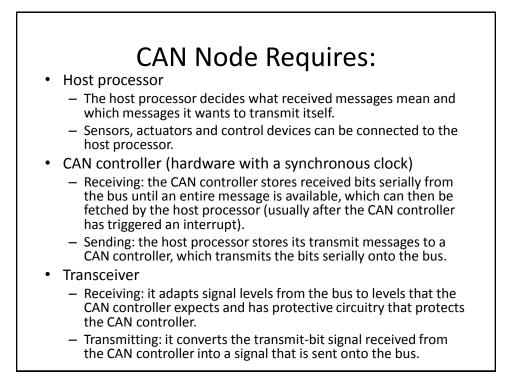

- The CAN bus (Controller Area Networking) was defined in the late 1980 by Bosch, initially for use in automotive applications. It has been found to be very useful in a wide variety distributed industrial systems

- Characteristics:

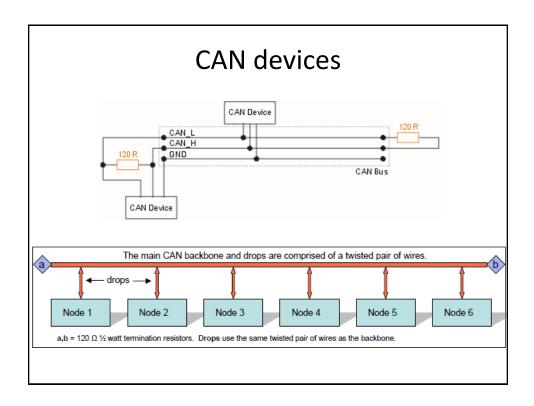

- Uses a single terminated twisted pair cable

- Is multi master

- Maximum Signal frequency used is 1 Mbit/sec

- Length is typically 40M at 1Mbit/sec up to 10KM at 5Kbits/sec

- Has high reliability with extensive error checking

- Typical maximum data rate achievable is 40KBytes/sec

- Maximum latency of high priority message <120 µsec at 1Mbit/sec

## Signal characteristics

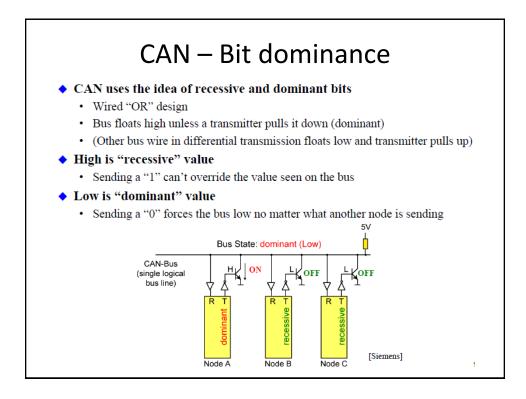

- CAN may be implemented over a number of physical media (most common is a twisted pair of wires) so long as the drivers are open-collector and each node can hear itself and others while transmitting (this is necessary for its message priority and error handling mechanisms)

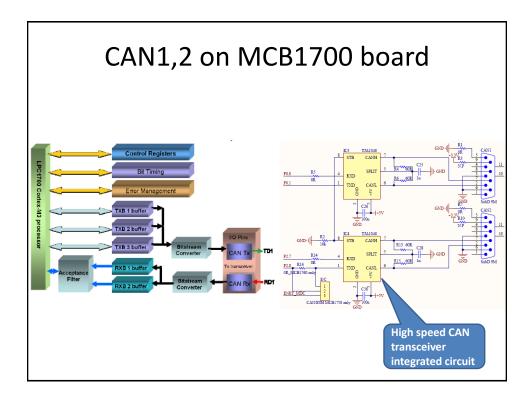

- The most popular transceiver chips:

Philips 82C251

- TJA1040 (on MCB1700 evaluation board)

- It is necessary to terminate the bus at both ends with 120 Ohms

- prevent reflections

- unload the open collector transceiver drivers

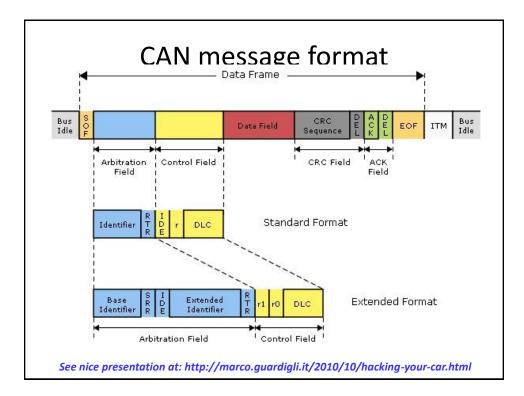

| CAN message format                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                      |                                                                                                             |               |         |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------|---------|--|--|--|--|

| SOF MESSAGE I                                                                                                                                                                                                                         | RTR CONTROL                                                                                                                                                                                                                                                                                                          | DATA                                                                                                        | CRC           | ACK EOF |  |  |  |  |

| <ul> <li>its length is</li> <li>Remote Transr</li> <li>Control field (</li> <li>specifies the</li> <li>Data Field (DAI</li> <li>CRC field cont</li> <li>Acknowledge f</li> <li>an empty sl</li> <li>it does NOT one node o</li> </ul> | (SOF)<br>ifier (MID)<br>he value the Higher the p<br>either 11 or 29 bits long on<br>nission Request (RTR)=<br>CONTROL)<br>e number of bytes of data<br>TA) length 0 to 8 bytes<br>aining a fifteen bit cycl<br>field (ACK)<br>ot which will be filled by a<br>say that the node you into<br>n the whole network got | depending on the s<br>0<br>1 to follow (0-8)<br>ic redundancy ch<br>any and every node<br>ended the data fo | ethat receive | ng used |  |  |  |  |

| End of Frame (                                                                                                                                                                                                                        | EOF)                                                                                                                                                                                                                                                                                                                 |                                                                                                             |               |         |  |  |  |  |

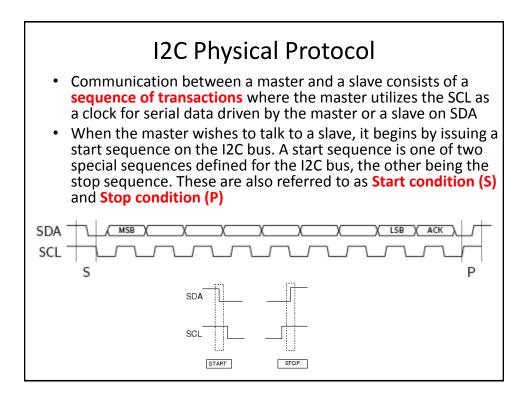

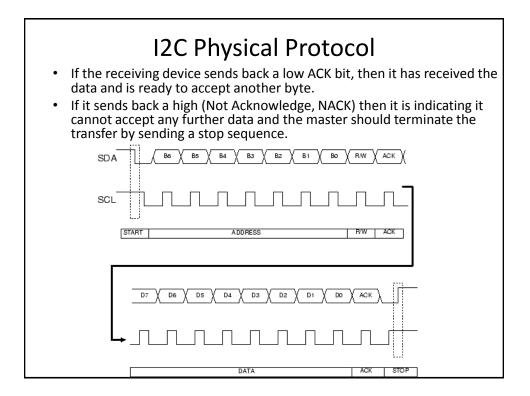

| I2C Physical Protocol                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

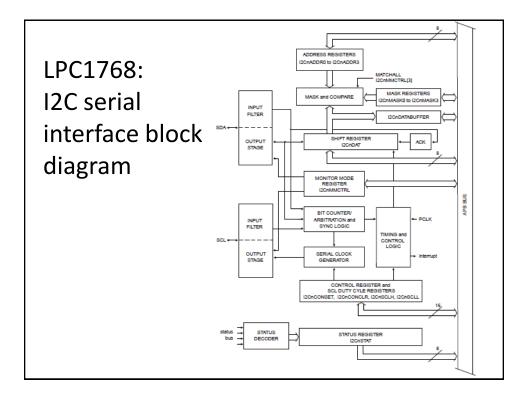

| <ul> <li>A transaction consists of a sequence of bytes.</li> <li>Each byte is sent as a sequence of 8 bits.</li> <li>The bits of each byte of data are placed on the SDA line starting with the MSB. The SCL line is then pulsed high, then low.</li> <li>For every 8 bits transferred, the device receiving the data sends back an acknowledge bit, so there are actually 9 SCL clock pulses to transfer each 8 bit byte of data.</li> </ul> |

| SDA D7 D6 D5 D4 D3 D2 D1 D0 ACK                                                                                                                                                                                                                                                                                                                                                                                                               |

| SCL1_2_3_4_5_6_7_8_9                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Data tr       | ansfer | from | mast | er to s | slave |

|---------------|--------|------|------|---------|-------|

| START ADDRESS | W ACK  | DATA | ACK  | DATA    | ACK P |

| sent by ma    |        |      |      |         |       |

| Data tr        | ar | nsfe | er from s | lav | e to mas | ter  |   |

|----------------|----|------|-----------|-----|----------|------|---|

| START ADDRESS  | R  | ACK  | DATA      | ACK | DATA     | NACK | Р |

| sent by master |    |      |           |     |          |      |   |

## Speed

- Standard clock speeds:

- 100kHz

- 10kHz

- However, the standard lets us use clock speeds from zero to 100kHz

- A fast mode is also available (400kHz Fast mode)

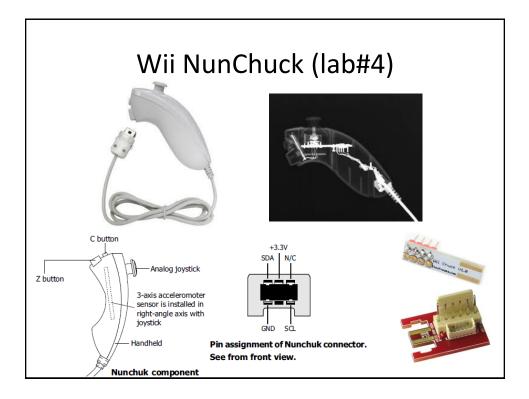

| Wii Nu          | unChuck Ir                        | nternals                           |  |

|-----------------|-----------------------------------|------------------------------------|--|

| Function        | Hardware                          | Circuit board surface and mounting |  |

| с               | membrane switch                   | daughterboard, through-<br>hole    |  |

| z               | membrane switch                   | daughterboard, through-<br>hole    |  |

| Joystick X      | axial potentiometer, 30KΩ         | through-hole                       |  |

| Joystick Y      | axial potentiometer, $30K\Omega$  | through-hole                       |  |

| Accelerometer   | ST 8XRJ 3L02AE 820 MLT            | surface mount, top                 |  |

| Microcontroller | FNURVL 405 849KM (48-<br>pin QFP) | surface mount, bottom              |  |

| http://wii      | brew.org/wiki/Nunchuc             | k#Nunchuk                          |  |

### Wii NunChuck Internals

- Joystick: axial potentiometer, 30KΩ through-hole

- Accelerometer: ST 8XRJ 3L02AE 820 MLT surface mount, top

- Microcontroller: FNURVL(A)-405 849KM (48-pin QFP) surface mount, bottom

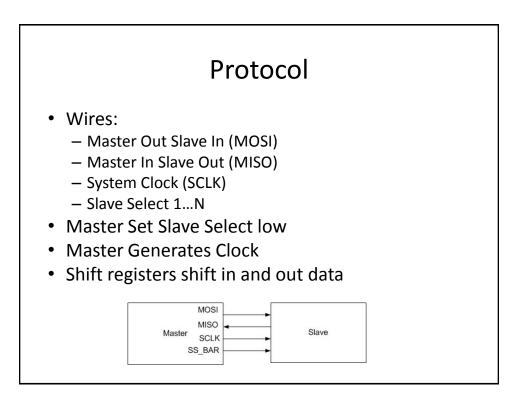

## **SPI Basics**

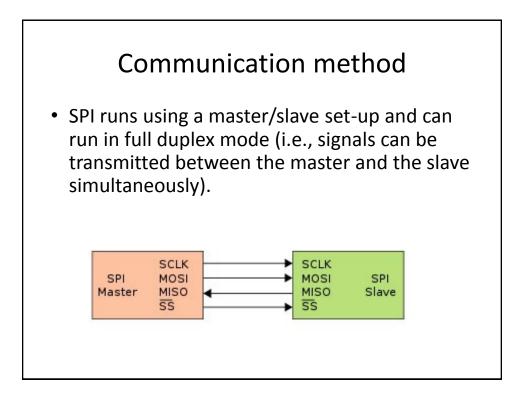

- Serial Peripheral Interface (SPI) is a simple serial communication method/protocol using 4 wires

- Also known as a 4 wire bus

- Used to communicate across small distances

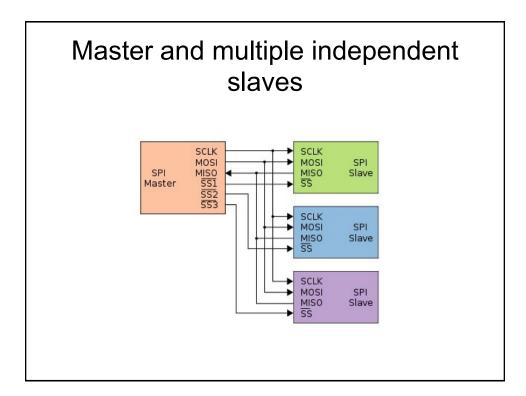

- Multiple Slaves, Single Master

- Synchronized

#### SPI

- Fast, Easy to use, Simple

- Everyone supports it

- Has some advantages over I2C

- SPI can communicate at much higher data rates than I2C.

- Also, when multiple slaves are present, SPI requires no addressing to differentiate between these slaves.

### Capabilities of SPI

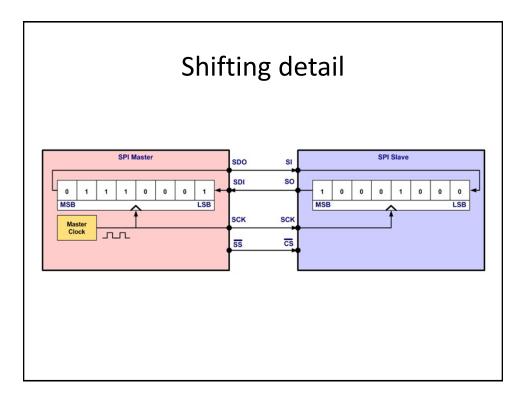

- Always Full Duplex

- Communicating in two directions at the same time

- Transmission need not be meaningful

- Multiple Mbps transmission speed

- Transfers data in 4 to 16 bit characters

- Multiple slaves

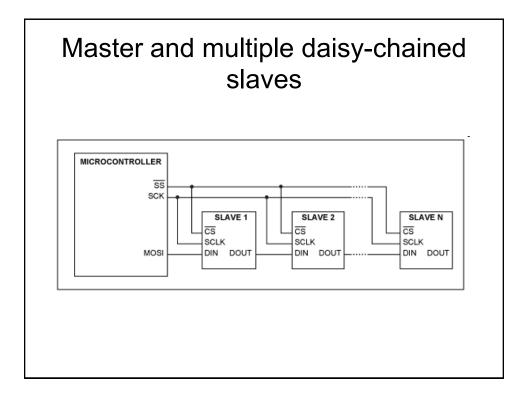

- Daisy-chaining possible

| Summary         |                 |                     |                                           |                                                           |                                                                                                                                         |                                                                                                                                                                                    |

|-----------------|-----------------|---------------------|-------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comm.<br>method | Shares<br>clock | Num.<br>of<br>wires | Speed                                     | Dist                                                      | Pros                                                                                                                                    | Cons                                                                                                                                                                               |

| UART            | No              | 2                   | 115Kbits/sec<br>max                       | Medium,<br>long                                           | Simple;<br>Widely supported;<br>Large range of physical standard<br>interfaces (TTL, RS-232, RS-422,<br>RS-485);                        | It's asynchronous;<br>Requires reasonable clock accuracy at both<br>ends;                                                                                                          |

| CAN             | No              | 3                   | 1 Mbits/sec                               | Long:<br>40m<br>(1Mbit/sec)<br>up to 10km<br>(5Kbits/sec) | Highly reliable;<br>Reduces amount of wiring;<br>Multi-master capability;                                                               | Complex;                                                                                                                                                                           |

| 12C             | Yes             | 2                   | 100Kbits/sec<br>400Kbits/sec<br>fast mode | Short,<br>medium<br>(< 6")                                | Simple;<br>Multi-master capability;<br>Only 2 wires to support multiple<br>devices;<br>Robust in noisy or power-<br>up/down situations; | More complex protocol than SPI;<br>Harder to level-shift or optoisolate due to<br>bidirectional lines;<br>Need for pull-up resistors can reduce power<br>efficiency in some cases; |

| SPI             | Yes             | 4                   | 10-20Mbits/sec                            | Short                                                     | Fast, easy, simple;<br>A lot of support;<br>Self clocking;<br>Flexible data word sizes;                                                 | Multiple devices need multiple select lines;<br>No acknowledgement ability;<br>No inherent arbitration;<br>No flow control;<br>Single master only;                                 |

#### Credits, References

- <u>http://www.ece.cmu.edu/~ece649/lectures/11\_can.pdf</u>

- <u>http://marco.guardigli.it/2010/10/hacking-your-car.html</u>

- <u>http://www.esd-electronics-usa.com/Controller-Area-Network-CAN-Introduction.html</u>

- <u>http://www.ni.com/white-paper/2732/en</u>

- <u>http://www.best-microcontroller-projects.com/i2c-tutorial.html</u>

- <u>http://www.robot-electronics.co.uk/acatalog/I2C\_Tutorial.html</u>

- <u>http://www.ee.nmt.edu/~teare/ee308l/datasheets/S12SPIV3.pdf</u>

- http://www.eecs.umich.edu/courses/eecs373/refs.html

- Jonathan W. Valvano, Embedded Systems: Introduction to Arm Cortex-M3 Microcontrollers, 2012. (Chapter 8)